Louisiana Tech University

## Louisiana Tech Digital Commons

Master's Theses

**Graduate School**

Summer 8-2020

# The Megaprocessor as an Educational Tool Making the Abstract Concrete

Jonathon Beauregard II

Follow this and additional works at: https://digitalcommons.latech.edu/theses

Part of the Computer Sciences Commons

#### **Recommended Citation**

Beauregard, Jonathon II, "" (2020). *Thesis*. 44. https://digitalcommons.latech.edu/theses/44

This Thesis is brought to you for free and open access by the Graduate School at Louisiana Tech Digital Commons. It has been accepted for inclusion in Master's Theses by an authorized administrator of Louisiana Tech Digital Commons. For more information, please contact digitalcommons@latech.edu.

## THE MEGAPROCESSOR AS AN EDUCATIONAL TOOL:

## MAKING THE ABSTRACT CONCRETE

by

Jonathon Beauregard II, B.S.

A Thesis Presented in Partial Fulfillment of the Requirements of the Degree Master of Science

### COLLEGE OF ENGINNERING AND SCIENCE LOUISIANA TECH UNIVERSITY

August 2020

### LOUISIANA TECH UNIVERSITY

#### **GRADUATE SCHOOL**

April 22, 2020

Date of thesis defense

We hereby recommend that the thesis prepared by

Jonathon Wayne Beauregard II, B.S

entitled The Megaprocessor as an Educational Tool

Making the Abstract Concrete

be accepted in partial fulfillment of the requirements for the degree of

Master of Science in Computer Science

Dr. Jean Gourd Supervisor of Thesis Research

Dr. Pradeep Chowriappa, Head of Computer Science

Members of the Thesis Committee: Dr. Jean Gourd Dr. Box Leangsuksun Dr. Ben Choi

**Approved:**

Hisham Hegab Dean of Engineering & Science

Approved:

ann

Ramu Ramachandran Dean of the Graduate School

### ABSTRACT

Computer architecture courses can be difficult for students to engage with and learn from. This is because, unlike most core courses for a computer science student, learning architecture is an abstract process. To address this, universities have implemented methods for teaching course material other than purely descriptive methods. This typically means using simulations to model some aspect of a CPU or FPGA (fieldprogrammable gate array) boards for hands-on experimentation in CPU design. However, there are issues with these tools. Simulations can only cover a few topics well, are prone to being abandoned, and introduce additional abstraction layers. FPGAs, while great for advanced topics and long class projects, are often best suited for senior and graduate level students. Both methods are useful, but neither offers a tangible learning experience, which is what the Megaprocessor can provide. The Megaprocessor is a room sized, general-purpose computer made from discrete components, whose architecture is comprised of primitive logic gates with LEDs on every input and output. The entire circuitry of the Megaprocessor is transparent to the users, with its entire state visible and unabstracted. Because of these properties, it is a great learning mechanism for computer architecture education. The Megaprocessor is a tool for hands on and project-based learning that can be used to span the learning gap between simulations and FPGAs.

## APPROVAL FOR SCHOLARLY DISSEMINATION

The author grants to the Prescott Memorial Library of Louisiana Tech University the right to reproduce, by appropriate methods, upon request, any or all portions of this Thesis. It is understood that "proper request" consists of the agreement, on the part of the requesting party, that said reproduction is for his personal use and that subsequent reproduction will not occur without written approval of the author of this Thesis. Further, any portions of the Thesis used in books, papers, and other works must be appropriately referenced to this Thesis.

Finally, the author of this Thesis reserves the right to publish freely, in the literature, at any time, any or all portions of this Thesis.

Author \_\_\_\_\_

Date \_\_\_\_\_

## **DEDICATION**

This thesis is dedicated to my wife, Rachel. I would not be where I am today without her, academically or professionally. She helped me to see something in myself that I would never have seen otherwise. She inspired me to pursue academia and to be a better version of myself. I am forever thankful.

# TABLE OF CONTENTS

| ABSTRACTiii                                            |

|--------------------------------------------------------|

| APPROVAL FOR SCHOLARLY DISSEMINATION iv                |

| DEDICATIONv                                            |

| LIST OF FIGURES xii                                    |

| LIST OF TABLES xiv                                     |

| ACKNOWLEDGMENTS xv                                     |

| CHAPTER 1 INTRODUCTION 1                               |

| 1.1 The Current State of Computer Architecture Courses |

| 1.2 An Overview of the Megaprocessor                   |

| 1.3   Building a Megaprocessor                         |

| 1.4 The Organization of This Thesis                    |

| CHAPTER 2 THE MEGAPROCESSOR 4                          |

| 2.1 Details of the Megaprocessor                       |

| 2.1.1 Design                                           |

| 2.1.2 Gates                                            |

| 2.1.3 Boards                                           |

| 2.1.4 Modules                                          |

| 2.1.5 Frames                                           |

| Arithmetic and Logic Unit (ALU)7                       |

| State and Status                                       |

| General Purpose Registers                              |

| Inp     | at and Instruction Decoding                      | . 12 |

|---------|--------------------------------------------------|------|

| Spe     | cial Purpose Registers                           | . 13 |

| Me      | mory                                             | . 14 |

| Cor     | atrol and I/O                                    | . 15 |

| Cor     | nnectivity                                       | . 16 |

| 2.1.6   | Architecture                                     | . 16 |

| Inst    | ruction Set                                      | . 17 |

| Inst    | ruction Cycle                                    | . 20 |

| 2.1.7   | Highlights                                       | . 21 |

| 2.2 T   | The Need for the Megaprocessor                   | . 21 |

| 2.2.1   | Computer Architecture is an Abstract Class       | . 22 |

| 2.2.2   | Computer Architecture is a Difficult Class       | . 23 |

| 2.2.3   | Computers Are Perceived As a 'Magical Black Box' | . 23 |

| 2.3 V   | Vhat the Megaprocessor Provides                  | . 25 |

| 2.3.1   | Broken Down to Raise Visibility                  | . 25 |

| 2.3.2   | Uniquely Hands-On                                | . 26 |

| CHAPTER | 3 BACKGROUND                                     | . 27 |

| 3.1 C   | Guidelines                                       | . 27 |

| 3.1.1   | Curricula Recommendations                        | . 27 |

| 3.1.2   | Class Objectives                                 | . 28 |

| The     | Science of Computing III                         | . 28 |

| Dig     | ital Design                                      | . 28 |

| Cor     | nputer Architecture                              | . 29 |

| Adv     | vanced Computer Architecture                     | . 29 |

| 3.2 S   | imulations                                       | . 29 |

| 3.2.1  | Benefits of Simulations                    |  |

|--------|--------------------------------------------|--|

| 3.2.2  | 2 Gaps with Simulations                    |  |

| 3.2.3  | 3 Simulation at Louisiana Tech University  |  |

| 3.3    | FPGAs                                      |  |

| 3.3.1  | Excessive for Some Topics                  |  |

| 3.3.2  | 2 Great for Advanced Topics                |  |

| 3.4    | Architecture                               |  |

| 3.4.1  | Changing Course Content                    |  |

| 3.4.2  | 2 Using RISC-V                             |  |

| 3.5    | Novel Approaches                           |  |

| 3.6    | Megaprocessor                              |  |

| 3.6.1  | I Suitable Subjects                        |  |

| T      | he Science of Computing and Digital Design |  |

| С      | omputer Architecture                       |  |

| 3.6.2  | 2 Unsuitable Subjects                      |  |

| А      | dvanced Computer Architecture              |  |

| CHAPTE | ER 4 MEGAPROCESSOR BUILD PLANNING          |  |

| 4.1    | Establish Communication                    |  |

| 4.2    | Review Existing Documentation              |  |

| 4.3    | Create New Documentation                   |  |

| 4.4    | Find and Correct Errors                    |  |

| 4.5    | Place Orders                               |  |

| 4.6    | Creation of Simulations                    |  |

| CHAPTE | ER 5 BUILDING                              |  |

| 5.1    | Soldering                                  |  |

| 5.2    | Testing                                    | 41 |

|--------|--------------------------------------------|----|

| 5.3    | Laser Paneling                             | 43 |

| 5.4    | Metal Framing                              |    |

| 5.5    | Assembling                                 | 44 |

| 5.6    | Awakening                                  | 46 |

| CHAPTE | ER 6 PRELIMINARY RESULTS AND CONTRIBUTIONS | 47 |

| 6.1    | Board Designs                              | 47 |

| 6.2    | Parts List                                 | 48 |

| 6.2.1  | 1 Board Components                         | 48 |

| 6.2.2  | 2 Changes to LEDs                          | 51 |

| 6.2.3  | 3 Soldering                                | 53 |

| 6.2.4  | 4 Module Components                        | 53 |

| 6.2.5  | 5 Frame Components                         | 54 |

| 6.2.6  | 6 Part Count                               | 55 |

| 6.2.7  | 7 Metal Framing                            | 56 |

| 6.3    | Test Plans                                 | 60 |

| 6.4    | Build Plans                                | 61 |

| 6.5    | Digital Design Simulations                 | 62 |

| 6.6    | Open Repository for Distribution           | 62 |

| 6.7    | Researching Application to Education       | 63 |

| CHAPTE | ER 7 DISCUSSION                            | 64 |

| 7.1    | Digital Design                             | 64 |

| 7.2    | Computer Architecture                      | 65 |

| 7.2.1  | 1 Teacher Driven Lectures                  | 65 |

| 7.2.2  | 2 Student Interaction                      | 66 |

| 7.2.3   | Soldering Labs                                                   | . 66 |

|---------|------------------------------------------------------------------|------|

| 7.3 A   | ccessibility Solutions                                           | . 67 |

| 7.3.1   | Divide into Labs                                                 | . 67 |

| 7.3.2   | Photo and Video Repository                                       | . 67 |

| 7.4 Sc  | chematics and Design                                             | . 68 |

| 7.5 M   | egaprocessor Simulation                                          | . 68 |

| 7.6 M   | easuring the Effectiveness of the Megaprocessor in the Classroom | . 69 |

| 7.6.1   | Pedagogical Design                                               | . 69 |

| Com     | pare Sections                                                    | . 70 |

| Opti    | onal Additions                                                   | . 70 |

| CHAPTER | 8 CONCLUSION AND FUTURE WORK                                     | . 71 |

| 8.1 Co  | onclusions                                                       | . 71 |

| 8.2 Co  | ontributions of this Thesis                                      | . 72 |

| 8.3 Fu  | ature Work on Megaprocessor                                      | . 72 |

| 8.3.1   | Additional Registers                                             | . 73 |

| 8.3.2   | Bus Connection                                                   | . 73 |

| 8.3.3   | Larger Bus                                                       | . 73 |

| 8.3.4   | Instruction Set                                                  | . 74 |

| 8.3.5   | Redesign RAM                                                     | . 74 |

| 8.4 Fu  | uture Work on Megaprocessor I/O                                  | . 75 |

| 8.4.1   | Motherboard                                                      | . 75 |

| 8.4.2   | Display                                                          | . 75 |

| 8.4.3   | Keyboard Input                                                   | . 76 |

| 8.4.4   | Storage                                                          | . 76 |

| 8.5 Oj  | perating System                                                  | . 76 |

| 8.6    | Future Work on RISC-V               | . 77 |

|--------|-------------------------------------|------|

| 8.7    | Expand Circuit Simulations          | . 77 |

| 8.8    | Remote Access                       | . 78 |

| 8.9    | Cyber Security                      | . 78 |

| 8.10   | Game Design                         | . 78 |

| 8.11   | Conclusions Regarding Future Work   | . 79 |

| 8.12   | Final Remarks                       | . 79 |

| APPEN  | DIX A Diagrams                      | . 80 |

| A.1    | Megaprocessor Connectivity Diagrams | . 80 |

| BIBLIO | GRAPHY                              | 86   |

# LIST OF FIGURES

| Figure 2-1: A panorama photo of the Megaprocessor.    4                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 2-2:</b> 4x2 AND/OR PCB                                                                                                                                |

| <b>Figure 2-3:</b> Flag Calculation module                                                                                                                       |

| Figure 2-4: Layout of the processor frames. This excludes RAM and I/O                                                                                            |

| Figure 2-5: The ALU frame. There is a space between the two modules that separates them                                                                          |

| <b>Figure 2-6:</b> The ALU module diagram. Shows the boards and their connections within the module. Note: the bus connections are not present in module diagram |

| Figure 2-7: The ALU control module diagram. Note: the bus connections are not present in module diagram                                                          |

| Figure 2-8: State and Status frame                                                                                                                               |

| Figure 2-9: General Purpose Registers frame                                                                                                                      |

| Figure 2-10: Input and Instruction Decoding frame                                                                                                                |

| Figure 2-11: Special Purpose Registers frame                                                                                                                     |

| <b>Figure 2-12:</b> RAM frame                                                                                                                                    |

| Figure 2-13: Control and I/O frame                                                                                                                               |

| Figure 2-14: Typical processor layout                                                                                                                            |

| <b>Figure 2-15:</b> 0x40 is the add opcode. The 'D' means ADD R1, R3. The full instruction is 4D                                                                 |

| Figure 2-16: Information on the divide operation                                                                                                                 |

| Figure 2-17: Examples of Divide operation                                                                                                                        |

| Figure 2-18: Arcade stick connected to Control and I/O                                                                                                           |

| Figure 4-1: The 3-input AND simulation. The top section is the circuit, the bottom is the encapsulated component.       38                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 4-2:</b> The Full Adder simulation. The top section is the circuit, the bottom is the encapsulated component                                                                         |

| Figure 4-3: Transistor level RS Flip Flop                                                                                                                                                      |

| Figure 5-1: Test of laser printing of module graphic                                                                                                                                           |

| Figure 5-2: The front of the State Machine Frame                                                                                                                                               |

| Figure 5-3: The back of the State Machine Module                                                                                                                                               |

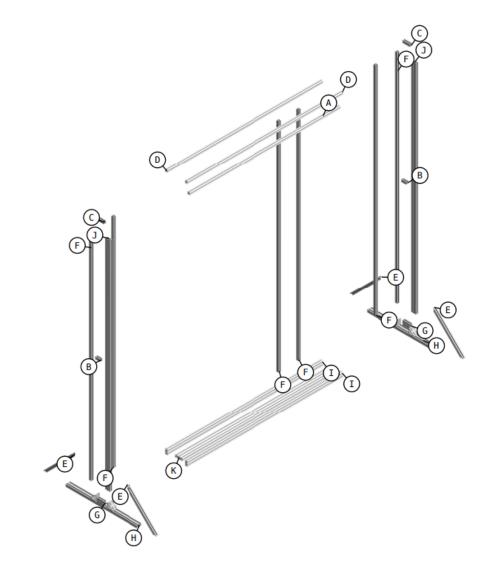

| Figure 6-1: Isometric view of metal frame                                                                                                                                                      |

| Figure 6-2: Exploded view of metal frame                                                                                                                                                       |

| Figure 6-3: Full build of materials, including price                                                                                                                                           |

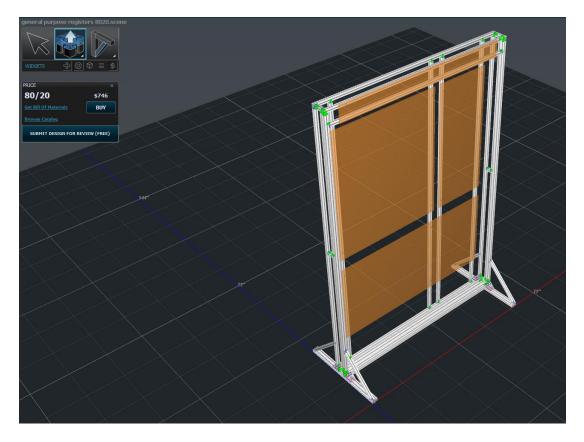

| Figure 6-4: Screenshot of 3-D model of General Purpose Registers frame                                                                                                                         |

| <b>Figure 6-5:</b> Build guide for the Services Board. Includes parts number, the original description from Mr. Newman, and additional information to make the build process a self-guided one |

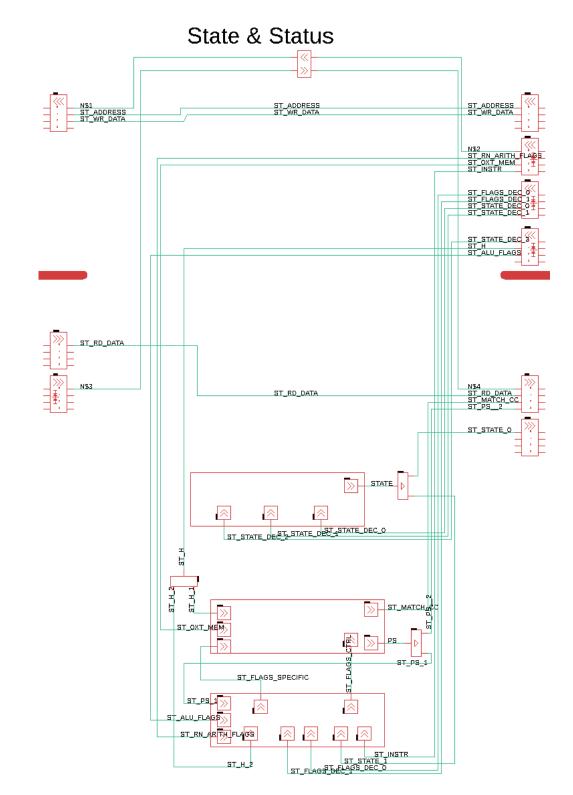

| Figure A-1: State and Status connectivity diagram                                                                                                                                              |

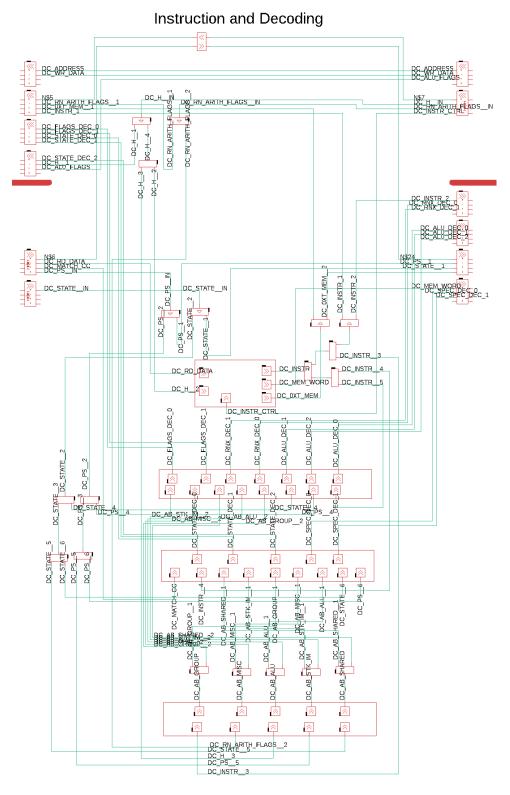

| Figure A-2: Instruction and Decoding connectivity diagram                                                                                                                                      |

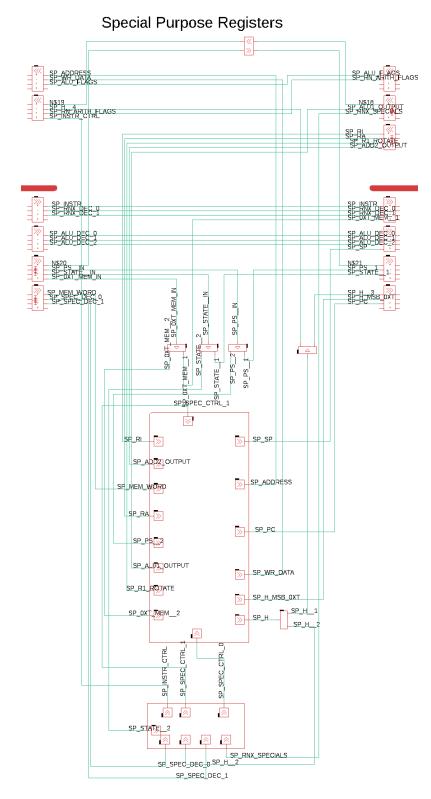

| Figure A-3: Special Purpose Registers connectivity diagram                                                                                                                                     |

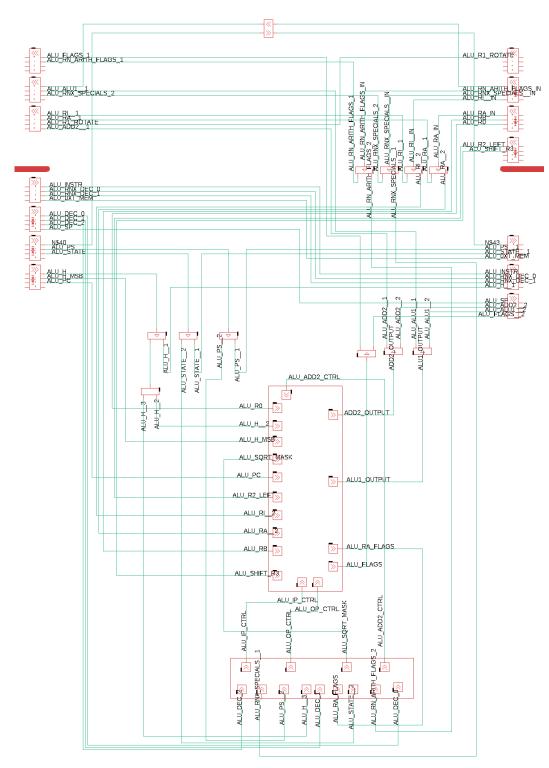

| Figure A-4: ALU connectivity diagram                                                                                                                                                           |

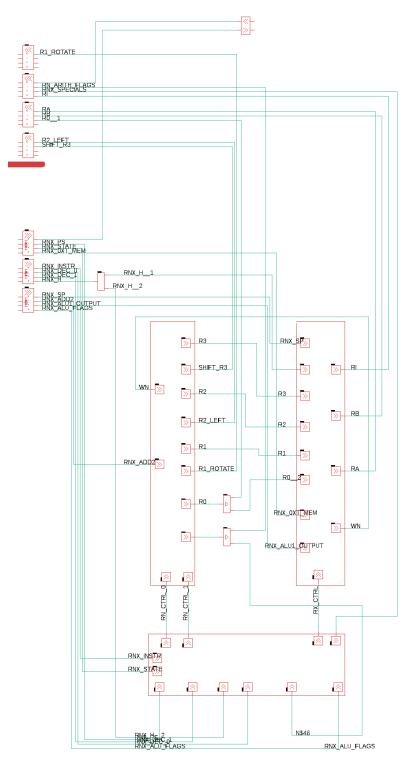

| Figure A-5: General Purpose Registers connectivity diagram                                                                                                                                     |

# LIST OF TABLES

| <b>Table 6-1:</b> Margin Calculations. This is not the full table, it is only a small segment4                                                                                            | 19 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Table 6-2:</b> Parts list for the 16-bit register board. The component names are simplified to fit here, and the full part names can be found in the documents in the open repository. | 50 |

| <b>Table 6-3:</b> Build information for all 16-bit register boards needed.                                                                                                                | 51 |

| Table 6-4: Red LEDs: 2mA, 1.7V.         5                                                                                                                                                 | 52 |

| Table 6-5: Green LEDs: 20mA, 2.1V.         5                                                                                                                                              | 52 |

| Table 6-6: Blue LEDs: 20mA, 3.5V.         5                                                                                                                                               | 53 |

| Table 6-7: Boards list for General Purpose Registers module                                                                                                                               | 54 |

| Table 6-8: Sample from parts list outside of board components.       4                                                                                                                    | 55 |

| Table 6-9: Sample from part counts for all boards.                                                                                                                                        | 56 |

### ACKNOWLEDGMENTS

First, I would like to thank my teacher and advisor, Dr. Jean Gourd. Without him this project would not have happened, and I would likely not have pursued my master's degree. Dr. Gourd helped secure funding, spearhead the project, and guide me through this journey.

I would also like to extend my gratitude to Mr. James Newman, the first person to design and build the Megaprocessor. His permission and encouragement allowed this project to happen. Mr. Newman provided assistance and additional documentation throughout the build process.

Finally, I am sincerely grateful for the help of my good friend and former manager, Dr. David Lippert. His input on this thesis was vital. He has mentored me through the years, and I am thankful for him. Without his support, pursuing my master's degree while working full-time would have been impossible.

### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1** The Current State of Computer Architecture Courses

Computer Architecture can be a difficult subject for students. The classes are often taught from dryly written books and slide decks featuring many diagrams that many students often just memorize. Course material is abstract and because students are used to hands-on programming they often struggle [9]. The subject matter is difficult to understand and learn for many students. Unlike other core courses, where coding and hands-on projects are used, computer architecture lacks an intuitive project-based learning approach. Even if the course does not use a purely descriptive teaching method, there is still the issue of finding appropriate tools that allow students to interact with computer architecture concepts. Most solutions used at universities are typically simulations and FPGAs. Simulations of ranging functionality, from digital circuit design to full CPU emulation, have been designed and used for teaching. FPGA boards can be used for class projects and labs; however, there are issues with both tools. Simulations are often specialized to cover one or two topics, and FPGAs are only well suited for advanced topics. The Megaprocessor offers a solution for these issues.

#### **1.2** An Overview of the Megaprocessor

The Megaprocessor is a general-purpose computer that is designed and built to maximize learning potential. All the components of the processor are built by hand using primitive logic gates, with each gates' input and output displayed with LEDs. This means that the entire processor is fully accessible and visible. All functionality and the full state of the processor are exposed with no interpretation layer. The Megaprocessor is a great educational tool for teaching computer architecture because it provides a learning experience that students get nowhere else. It truly allows them to see how a microprocessor works.

#### **1.3 Building a Megaprocessor**

The process of building a Megaprocessor at Louisiana Tech University is ongoing. Mr. James Newman was contacted for permission to use his designs at Louisiana Tech University. He was supportive, gave his permission, and provided additional documents. Unfortunately, there were many gaps in the documentation that prevented the immediate purchase of parts. This necessitated a reverse engineering of the Megaprocessor. The build phase is ongoing, and several inevitable setbacks occurred that have delayed the project. The build is anticipated to take at least another year before the Megaprocessor is fully operational. It took over two years of work to get to the build phase. All the work that was done to create a comprehensive parts list and build guide can be found in chapter six. Additionally, all contributions and documentation will be placed in an open repository to save others the time and effort involved in reverse engineering the Megaprocessor.

#### **1.4** The Organization of This Thesis

In the second chapter the Megaprocessor is introduced in greater detail, the issues with computer architecture education that it solves are examined, and its most significant qualities are presented. In the third chapter the relevant research that others have done is discussed, as well as the tools currently in use and how they fall short. The fourth chapter contains details about the reverse engineering phase. The fifth chapter covers the build process, both what has been done and has yet to be done. Chapter six discusses the output of this project and specifies the contributions which advance the state of the art. Chapter seven discusses how the Megaprocessor can be applied to various computer architecture courses. Finally, chapter eight contains conclusions and ideas for future work.

## **CHAPTER 2**

## THE MEGAPROCESSOR

#### 2.1 Details of the Megaprocessor

#### 2.1.1 <u>Design</u>

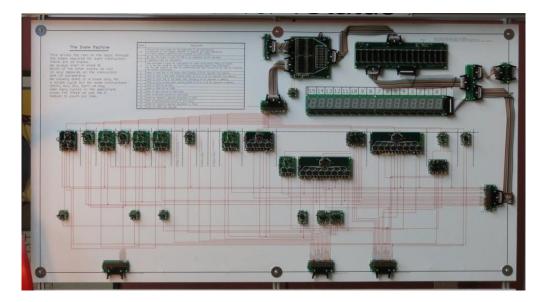

The Megaprocessor is a general-purpose processor, built using discrete transistors, resistors, and LEDs. Instead of a processor on a silicon wafer, the Megaprocessor is built out of PCBs (printed circuit boards), ribbon cables, and metal framing. Processors are normally made to take up as little space as possible, while the Megaprocessor takes up 20 square meters. It is fully handmade, with over 200,000 solder joints, and over 100,000 components. It consists of seven frames, each of which contains modules that encapsulate some logical CPU component as shown in (**Figure 2-1**) [27].

Figure 2-1: A panorama photo of the Megaprocessor.

Each module is a collection of boards that are decomposed down to primitive logic gates, other than the Control and I/O frame.

#### 2.1.2 <u>Gates</u>

Like all processors, the Megaprocessor's primitive logic gates are made from transistors and other components. What is unique about the Megaprocessor is that each gate has an LED on every input and output. This gives unprecedented insight into how the processor works. Every bit can be traced, and the state of the circuits within the processor are fully readable. The gates are also large enough to be read clearly by an observer, which makes for an exceptionally low density of components.

#### 2.1.3 <u>Boards</u>

PCBs (printed circuit boards) are the basic building block of the Megaprocessor. The circuitry is silkscreened on each PCB so that students and observers can read them and understand each component's connections, an example is shown in (**Figure 2-2**) [28]. A silkscreen is typically a white graphic overlay showing the circuit design and labels that is printed on a PCB. The PCBs are soldered by hand and have varying levels of complexity. There are PCBs that contain exactly one gate, and there are PCBs that are more complex, made of many gates and other components.

Figure 2-2: 4x2 AND/OR PCB.

### 2.1.4 <u>Modules</u>

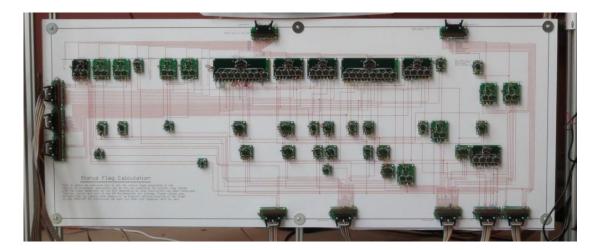

The boards come together to create modules which function as a component of a processor, like an ALU. There are fourteen modules not counting RAM and I/O. Each module is comprised of gates, ribbon cables, and wires to connect the gates and other PCBs, as well as a module graphic. The module graphic contains the entire circuit diagram showing all connections and text describing the functionality of the module, an example can be seen in (**Figure 2-3**) [29].

Figure 2-3: Flag Calculation module.

#### 2.1.5 <u>Frames</u>

The Megaprocessor is comprised of seven frames connected by ribbon cables that carry the bus signals. The frames come together to create the completed Megaprocessor. Each frame has a different function and is described below. The layout of the processor frames are shown in (**Figure 2-4**) [30].

| State & Status | Input & Decoding | Special Purpose Registers | Arithmetic & Logic Unit | General Purpos | e Registers |

|----------------|------------------|---------------------------|-------------------------|----------------|-------------|

| State Machine  | Fetch & Instr    | Special Registers         | ALU                     | Rn Reg         | Rx<br>Mux   |

| Status Reg     | Decode B         |                           |                         |                |             |

| Flag Calc      | Decode A         | Special Control           | ALU Control             | Box C          |             |

| Thay Galo      | Decode Opcode    |                           |                         | Rnx Control    |             |

Figure 2-4: Layout of the processor frames. This excludes RAM and I/O.

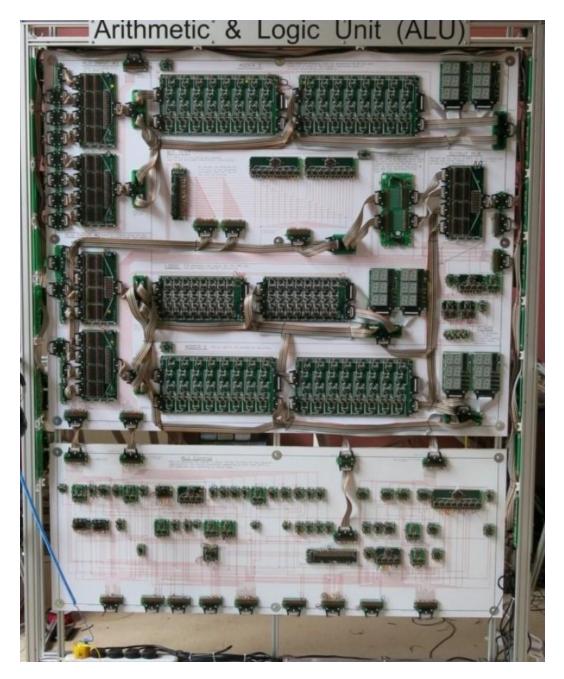

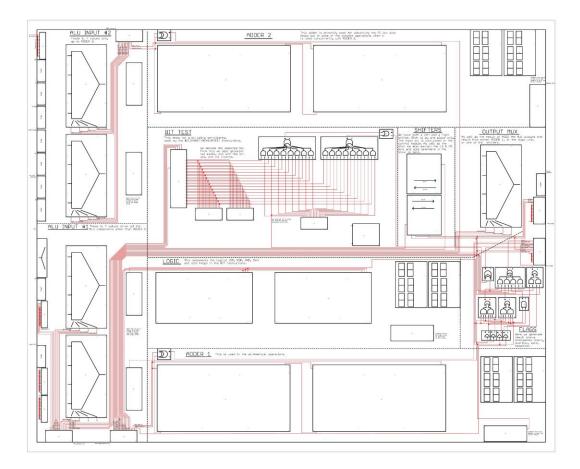

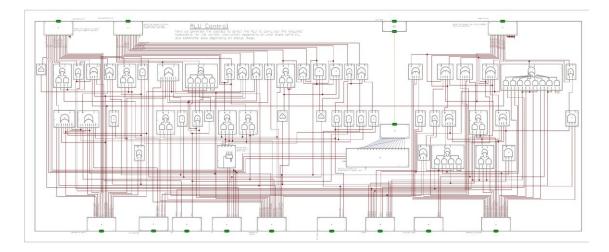

#### Arithmetic and Logic Unit (ALU)

This frame is divided into two modules as shown in (**Figure 2-5**) [27]. The ALU module is at the top of the frame (**Figure 2-6**), and the ALU control module is beneath it (**Figure 2-7**) [29]. Decoding the operation code to instruct the ALU on what operation to perform takes place on another frame. The negative, zero, and overflow flags generated by the ALU are sent to the Status Flags Calculation Module. A connectivity diagram for the ALU frame can be viewed in (**Figure A-4**) [27].

Figure 2-5: The ALU frame. There is a space between the two modules that separates them.

**Figure 2-6:** The ALU module diagram. Shows the boards and their connections within the module. Note: the bus connections are not present in module diagram.

Figure 2-7: The ALU control module diagram. Note: the bus connections are not present in module diagram.

### State and Status

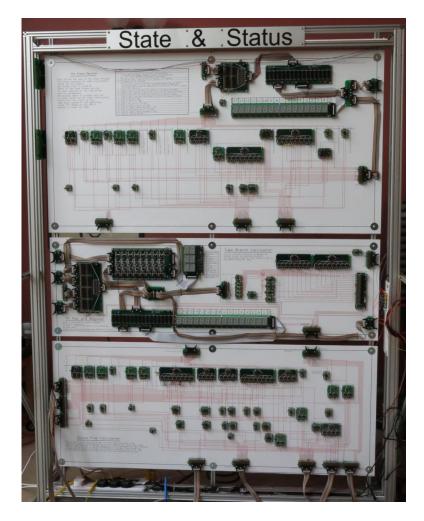

The State and Status frame is composed of three modules (**Figure 2-8**) [27]. The top module is the State Machine module, which keeps track of what the CPU is currently doing and orchestrates what state the processor will go into next given the current state, flags, and outputs. The middle module is the Status Register which contains bits that inform the State Machine module. The bottom is the State and Flag Calculation module, which calculates the bits stored in the Status Register. These modules come together to create the state machine of the processor [31].

Figure 2-8: State and Status frame.

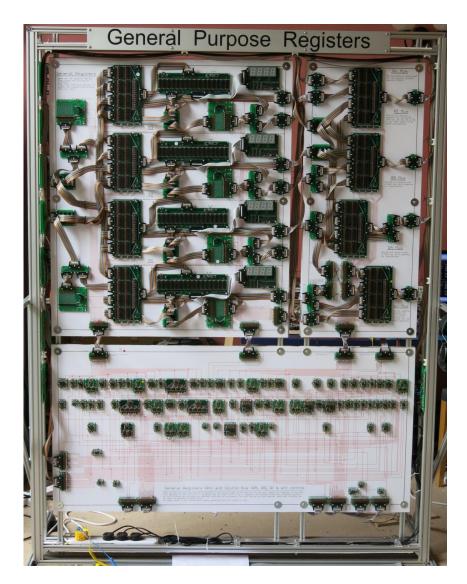

## General Purpose Registers

This frame consists of three modules: the General Register module which contains four registers, the General Register Multiplexer module which contains the multiplexes for the registers, and the General Register Control module as seen in (**Figure 2-9**) [27].

Figure 2-9: General Purpose Registers frame.

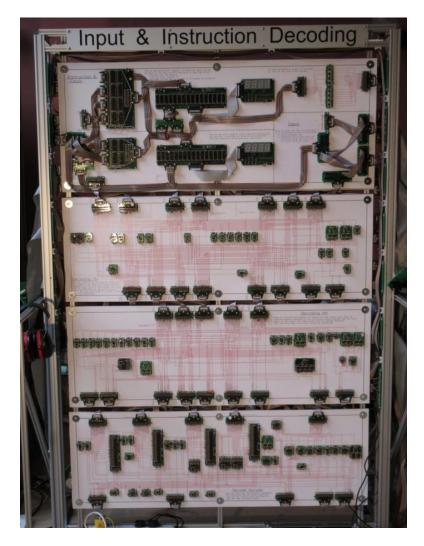

#### Input and Instruction Decoding

The Input and Instruction Decoding frame shown in (**Figure 2-10**) consists of four modules, one which handle decoding the instructions and another that decodes the operation codes (or opcodes). The other two modules generate control signals for the other frames. Based on the current opcode, different control signals will be sent. These control signals prepare the other frames for the instruction. For example, it may make different registers available to the ALU.

Figure 2-10: Input and Instruction Decoding frame.

### Special Purpose Registers

The Special Purpose Registers frame consists of two modules seen in (**Figure 2-11**) [27]. The Special Registers module contains the stack pointer, external address, and program counter as well as their associated multiplexors. The lower module is the Special Register Control, which generates control signals.

Figure 2-11: Special Purpose Registers frame.

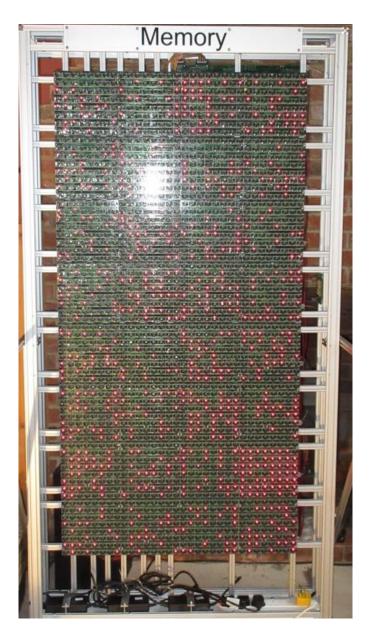

## <u>Memory</u>

The Memory frame shown in (**Figure 2-12**) contains 256 Bytes of RAM [27]. Each of the 2,048 total bits of RAM is illuminated with an LED. It can also function as a dot matrix display of 32 by 64 pixels, depending on the program and desired functionality.

Figure 2-12: RAM frame.

#### Control and I/O

More complex parts were used in the design and creation of the Control and I/O frame shown in (**Figure 2-13**) [27]. Part of the function of this frame is to be a side-by-side simulation of the Megaprocessor. The simulation compares its simulated output to the Megaprocessor's actual output. Should there be a difference, it halts the machine and dumps register values for debugging purposes. There is also a laptop that connects to the frame over serial interface to a control board to load programs to run on the Megaprocessor. The Megaprocessor simulation can be downloaded and used by students or faculty on their own computers for testing and learning.

Figure 2-13: Control and I/O frame.

#### **Connectivity**

There is a diagram showing the connections between major components for the processor frames located in (**Figure A-1**), (**Figure A-2**), (**Figure A-3**), (**Figure A-4**), and (**Figure A-5**) [27]. Each frame will have its own image, and to create the full diagram, they can be laid side-by-side in the correct order.

The frames are connected to each other in series (see **Figure 2-4**) [30]. The States and Status frame connects to the Input and Decoding frame, and any data directed to other frames down the line get forwarded and manipulated by the frames it travels through.

#### 2.1.6 <u>Architecture</u>

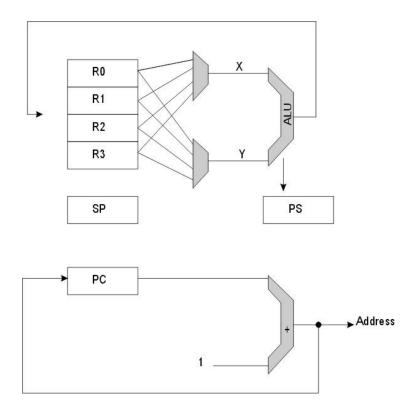

The Megaprocessor is a 16-bit processor with four general purpose registers (R0, R1, R2, R3) and three specialized registers: the program counter (PC), the stack pointer (SP), and the processor status register (PS). The components within the processor are connected using multiplexors that the Megaprocessor can configure to change the data paths depending on different instructions. The general layout of the processor is described in (**Figure 2-14**) [30].

Figure 2-14: Typical processor layout.

While most instructions can use any register, there are slight restrictions to the process flow. For example, RAM based instructions have limitations on register usage. R0 or R1 may only be used as source or destination for the data being moved to and from RAM, and R2 or R3 store the index of the RAM location.

#### Instruction Set

The instruction set consists of 8-bit opcodes with up to two bytes of additional data. This additional data designates which registers are being used, where the new value will be stored, or if it is a sub -operation. There are a total of 256 possible instructions, and all are allocated for some use. An instruction is read from memory and sent to be decoded. Depending on the instruction, the processor will be configured to fulfill the

instruction. For most instructions, the first register is the destination and the second is the source.

An example of one of the instructions is the addition opcode 0x40 seen in (**Figure 2-15**) [32]. The two bytes that follow the opcode designate what two registers are being added, with the first register being where the new value is ultimately stored. Of note for this instruction is that it takes one clock cycle to complete. In the example, R3 is being added to R1. R1 contains the hex value 848B and R3 contains the value A6AB. These values added together are 12B36. This is greater than what can be stored in the register, so the overflow flag (V) and carry flag (C) are turned on, and 2B36 is stored in R1.

#### ADD RA, RB

Operation:  $RA + RB \Rightarrow RA$

Format:

| 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|---|---|---|---|---|---|---|

| Code = 0x4, ADD |   | R | B | R | A |   |   |

Length/Cycles: 1 byte, 1 cycle Condition Codes: I - Not affected N \* Set if MSB set, cleared otherwise Z \* Set if result is zero, cleared otherwise V \* Set if overflow is generated. Cleared otherwise X \* As per carry bit. C \* Set if carry is generated. Cleared otherwise Example: R0[0000] R1[848B] R2[FFFF] R3[A6AB] PC[0075] SP[233B] PS[43(....NID.)] 0074: 4D: ADD R1,R3 R0[0000] R1[2B36] R2[FFFF] R3[A6AB] PC[0076] SP[233B] PS[79(CXV..ID.)]

**Figure 2-15:** 0x40 is the add opcode. The 'D' means ADD R1, R3. The full instruction is 4D.

Multiplication, division, and square root operations are implemented by iteration.

The following figures (Figure 2-16) and (Figure 2-17) provide information on the

division instruction [32] Unlike addition, which gets the opcode of 0x40, division is only comprised of two sub operations: 0xFA and 0xFB.

#### DIVS & DIVU

```

Operation:

if (R1 == 0)

execute TRAP 1

else

Quotient (R0 / R1) \Rightarrow R2

Remainder (R0 / R1) \Rightarrow R3

end if

if (signed operation)

abs(R1) \Rightarrow R1

end if

```

Description: If R1 is zero then TRAP 2 is taken. Otherwise R0 / R1 is calculated. The quotient is put in R2, the remainder. The arithmetic condition flags are cleared. There are two ways of defining signed division, the difference lying in whether or not negative remainders are allowed. Both are implemented, the method used is controlled by the D flag.

|        | D = 0            | D = 1           |

|--------|------------------|-----------------|

| 13/3   | Q = 4, $R = 1$   | Q = 4, $R = 1$  |

| 13/-3  | Q = -4, $R = 1$  | Q = -4, $R = 1$ |

| -13/3  | Q = -4, $R = -1$ | Q = -5, $R = 2$ |

| -13/-3 | Q = 4, $R = -1$  | Q = 5, $R = 2$  |

In all cases the following holds: Dividend = (Quotient × Divisor) + Remainder

Format:

| 7                  | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|--------------------|---|---|---|---|---|---|-----|

| 0xF, miscellaneous |   |   |   | 1 | 0 | 1 | sgn |

Encoding:

|     | 0        | 1      |

|-----|----------|--------|

| sgn | unsigned | signed |

Length/Cycles:

1 byte, division by zero is 7 cycles, unsigned is 18 cycles, signed is 19 cycles

Condition Codes: I - Not affected N, Z, V, X, C - Set to zero

Figure 2-16: Information on the divide operation.

(Figure 2-17) illustrates several examples of the divide instruction [32]. All four

registers are used in this instruction: R0 is the numerator, R1 is the denominator, R2 is

the quotient, and R3 is the remainder.

```

Examples:

R0[000D] R1[0003] R2[0000] R3[0000] PC[0162] SP[8321] PS[02(...N..)]

0161: FA:DIV.U

R0[000D] R1[0003] R2[0004] R3[0001] PC[0163] SP[8321] PS[00(....)]

At the start of the operation R0=13, R1=3. After the calculation R2=4 (quotient) and

now R3=1 (remainder.

```

```

R0[000D] R1[FFFD] R2[0000] R3[0000] PC[0164] SP[8321] PS[00(.....)]

0162: FB:DIV.S

R0[000D] R1[0003] R2[FFFC] R3[0001] PC[0165] SP[8321] PS[00(.....)]

At the start of the signed division operation R0=13, R1=-3. After the calculation

R2=-4 and now R3=1.

```

```

R0[FFF3] R1[0003] R2[FFFC] R3[FFFF] PC[016A] SP[8321] PS[40(....D.)]

0169: FB:DIV.S

R0[FFF3] R1[0003] R2[FFFB] R3[0002] PC[016B] SP[8321] PS[40(....D.)]

At the start of the signed division operation with the signed encoding flag on (D flag

in PS), R0=-13, R1=3. After the calculation R2=-5 and now R3=2.

```

Figure 2-17: Examples of Divide operation.

#### Instruction Cycle

The Megaprocessor implements the same instruction cycle that traditional

processors do: fetch, decode, read from RAM, and execute. The program counter is to be

incremented at the end of the fetch cycle.

Additionally, there is some instruction pipelining that occurs within the

Megaprocessor. Simple processors only perform one step in the clock cycle at a time.

This is inefficient as each step of the clock cycle uses different portions of the processor,

leaving the rest of the processor completely unutilized. A technique that modern

processors utilize is instruction pipelining, where multiple steps of a clock cycle occur at

once. The processor is therefore doing work continuously. It has one stage of pipelining, in which the next instruction is fetched while the current one is being executed.

#### 2.1.7 <u>Highlights</u>

The Megaprocessor has a user-controlled clock speed that can be slowed down so that each step takes seconds to perform. It has a maximum speed of 20kHz. The maximum speed is limited due to the design of the simple ripple adder combined with the type of discrete transistors used. Mr. Newman suggested using a different type of resistor in the ALU which should raise the maximum speed a bit [30].

Additionally, the Megaprocessor can be halted at any time by pushing a button that allows the current state of the processor to be observed and analyzed. Observers may also step through the program to explore each step of the execution by pressing another button on the Control and I/O frame. Once close examination is finished, the program can be continued with the push of a third button. There are system executions that take many instruction steps to complete, such as the divide operation. Even these basic operations can be stepped through and observed at the student's pace.

Finally, the Megaprocessor is the size of a room, 10 meters long and 2 meters tall. It would be possible to arrange the frames to surround its observers, as if the students are inside of the processor. It holds the Guinness World Record for the largest microprocessor [8].

### 2.2 The Need for the Megaprocessor

As previously mentioned, there are shortcomings with the current methods used in computer architecture education. For the students who take them, classes can be abstract and difficult in ways that they have not previously experienced. Strong students who have benefited from hands-on methods in previous classes may find the abrupt switch to abstract learning difficult to adjust to [26].

There are teaching alternatives that go beyond books and diagrams that have been designed to try and resolve this issue. Academic methods for teaching computer architecture beyond a descriptive method will be discussed in chapter three.

# 2.2.1 <u>Computer Architecture is an Abstract Class</u>

Computer architecture, unlike most other core computer science classes, is full of concepts that cannot be explored by using software or writing code. Most other topics, including operating systems, object-oriented programming, computer networking, data mining, and cloud computing, can be learned in an interactive way by writing code or through direct interaction. It is not so easy to observe an ALU inside of a real processor and fully explore it as it operates.

Computer Architecture can be explored with software, but not natively. This software is a layer that can only illustrate concepts it was written to highlight. Because of this abstraction layer, some concepts may be hidden or difficult to grasp. Different software packages highlight different concepts and have different gaps, but none are complete. Simulations have been made that model various aspects of processors and computer hardware; however, these simulations often only cover one topic and can be difficult to run. Code is not a substitute for physical interaction in computer architecture. This concept will be discussed further in chapter three.

Because these classes discuss abstract subject matter, students often have difficulty engaging with them and thereby find them uninteresting [9]. The Megaprocessor provides them an accessible processor model to study that can help motivate them to develop an interest in computer architecture. A processor that students can see, interact with, and touch with their own hands, can go a long way toward making computer architecture classes less abstract.

# 2.2.2 <u>Computer Architecture is a Difficult Class</u>

Because the material in these classes is abstract, it can be difficult for students to learn. This may be especially true for students who excel with project-based learning. Generally, the classes are structured as lectures, and the material is presented through diagrams that students often memorize. Instead of using traditional learning methods, the Megaprocessor provides access to a fully transparent CPU so that students can 'get their hands dirty.' It supplements lectures by allowing teachers to walk through the actions of the processor, highlight important information, and allow students to explore the lecture material, making the abstract more concrete. The stop button on the Megaprocessor allows an instructor to pause the processor in a desired state and ask students what the CPU is going to do next, moving the instruction from a lecture to an engaging discourse. Instructors can also guide students to follow the bits as they move through the data and control paths, anticipating where a bit is going or what action it is going to cause. There are more opportunities for student driven discovery that leads to better grasp of the material [40].

# 2.2.3 <u>Computers Are Perceived As a 'Magical Black Box'</u>

It is not readily possible for a student to open a computer and tinker with the CPU. Getting any real idea of what a CPU does at any given time is generally unfeasible. Modern operating systems and processors run at blistering speeds, and the CPU mechanisms are abstracted into oblivion. Because of this, it is easy to think of a CPU as a brain and leave it at that. The issue with this analogy is that it gives students an excuse to avoid learning complex concepts. If it is as complex as a human brain, which science still does not fully understand, why struggle to understand it? The analogy is problematic, both because the CPU is not like a brain, and because it is not out of reach for students to understand. Processors are fully designed by talented teams of humans, and the building blocks used to create modern processors can be learned. The Megaprocessor can help students understand the fundamentals of a processor. With it as a visible, concrete model, students can keep that insight with them throughout their careers because the method of learning was so memorable and remarkable. The Megaprocessor's architecture is drastically simpler than what is in use today; however, it contains the building blocks of modern microprocessors. Most classes utilize simplified, academic models because they are easier to learn from. At the same time, these models should be as close as possible to the real thing. The Megaprocessor meets both standards.

Unlike software that can be downloaded, extracted, decompiled, and experimented on, hardware is more complex to interact with. It is best understood through hands-on interaction; however, ironically the physical components of a computer can be harder for students to interact with than the software. While students are unable to modify the Megaprocessor once it is built and running, they can run different programs to experiment with its functions, as well as change the running speed and stop the processor to get a better visual understanding of how bits flow through the system. They can see how it works, and not merely read about it. It provides an immersive experience for students.

# 2.3 What the Megaprocessor Provides

The Megaprocessor provides a truly hands-on experience that allows students to learn about computer architecture. It provides a physical, working, general purpose processor that is tangibly accessible to students. The model of the processor is decomposed into discrete components, in a form factor that students can interact with.

### 2.3.1 Broken Down to Raise Visibility

The entire Megaprocessor is broken down to the transistor level, with an LED on every input and output of each component. Any segment of the processor can be approached and viewed at this level of detail. Gates and transistors are encapsulated to boards and modules, but nothing is hidden or abstracted away. If you get close enough, you can see all the discrete parts that go into a component, whether it is a register, a bit of RAM, or the ALU. Unlike most others, this processor can be slowed down to a crawl. Programs can be halted and stepped through to the granularity of a single clock cycle. Every action of the Megaprocessor executing the code can be observed and understood.

It is possible to make an 8-bit processor on a series of breadboards; however, those use far more complicated parts and are not normalized to the same level as the Megaprocessor. The chips on the breadboard creating the CPU can be complex. For example, just a single integrated circuit alone may contain the ALU. It is not possible to observe those chips and see exactly what they are doing. They can be useful for gaining a high-level view of what is occurring in a processor, but the same can be said about the Megaprocessor.

25

# 2.3.2 <u>Uniquely Hands-On</u>

The Megaprocessor can provide a completely hands on way to learn about computer architecture, from basic to complex concepts. Students can not only interact with it by writing and running code, but also by seeing details of the processor down to every gate. There is nothing hidden or abstracted away, other than the I/O. The main interface is an arcade stick that contains a joystick and buttons that serve as input to the Megaprocessor as seen in (**Figure 2-18**) [33]. This input can be used to interact with instructor provided or student written programs. Assembly code can be written by the student and then run on an actual general-purpose processor.

Figure 2-18: Arcade stick connected to Control and I/O.

# **CHAPTER 3**

# BACKGROUND

# 3.1 Guidelines

Before the different solutions for improving computer architecture education are compared, the grounds of comparison for the solution's effectiveness must be established. Most research done in computer architecture education discusses both computer engineering and computer science courses. Louisiana Tech University (the school that the author of this thesis attends) does not offer a computer engineering major. Because of this, the scope of classes will be restricted to three computer science courses offered at Louisiana Tech University. There is a newer class offered that will be covered as well.

# 3.1.1 <u>Curricula Recommendations</u>

The ACM, together with IEEE, issued a set of curricula recommendations for computer science [6].Within the document that they released, there are many knowledge areas within the 'body of knowledge' that they deem should be covered [2]. Of interest is the Computer Architecture and Organization knowledge area, with acronyms AR within the guidelines document, and CAO in the larger body of research papers. Within the knowledge area of CAO there are many topics and learning outcomes. The knowledge area of CAO and its topics can be used as a metric against the Megaprocessor and help guide discussion of content in university courses.

#### 3.1.2 <u>Class Objectives</u>

#### The Science of Computing III

The Science of Computing III is a class at Louisiana Tech University that covers topics from CAO. It is part of the 'Living with Cyber' computing curriculum, which is the freshman year program that all computer science and cyber engineering students participate in. It has a project-based learning paradigm, and the contents of the courses are open to review here: https://coes.latech.edu/living-with-cyber/. Concepts from CAO are first introduced in The Science of Computing I; however, the first significant instruction on these topics take place in Science of Computing III.

According to the course syllabus [14], the following topics from CAO are covered: the fundamentals of signed and floating-point number; character representation in computers; and a basic understanding of how a computer is made (e.g., ALU, CPU, memory, I/O). This course covers topics other than CAO, and what it contains is very introductory.

#### <u>Digital Design</u>

This course is typically taken in a student's sophomore year in the undergraduate program. According to the course catalog [22], the following topics from CAO are covered: introduction to digital design techniques, Boolean algebra, combinational logic, minimization techniques, simple arithmetic circuits, programmable logic, sequential circuit design, registers, and counters.

#### Computer Architecture

This course is typically covered in a student's junior or senior year in the undergraduate program. According to the course catalog [23], the following topics from CAO are covered: architecture and organization of computer systems, including the processor, control unit and microprogramming; computer arithmetic; memory hierarchy and memory management; input/output; and instruction sets.

#### Advanced Computer Architecture

This course is typically covered in the graduate program. According to the course catalog [24], the following topics from CAO are covered: pipeline systems design, processor design techniques (concepts, analysis, performance comparison, implementation, and commercial processors), memory system design, and interconnection media.

### 3.2 Simulations

Simulations of digital circuitry or CPU operation have become the go-to solution for use in classrooms and labs in CAO courses. Instructors and institutions have often defaulted to simulations because they have become accepted as better than a purely descriptive approach [40]. There are many types of simulations used for teaching computer architecture, ranging from simulations of simple digital circuitry up to full computer emulation [35].

# 3.2.1 <u>Benefits of Simulations</u>

Simulations can be used as great tools to teach the fundamentals of computer architecture and digital design [9,15]. Simulations for entry level topics, such as circuit design, allow students to experiment and learn basic concepts without having to use other more complex tools that do not typically offer additional benefits [19]. These simpler simulations are often easier to setup and use, and serve as a learning tool with very low user friction [43]. Due to the complex and difficult nature of teaching computer architecture, attempts to develop other methods are abandoned for a simulation approach because it is more feasible [18,42].

### 3.2.2 <u>Gaps with Simulations</u>

Using computer simulations instead of a purely lecture based approach is an improvement; however, simulations typically have limitations that prevent them from being optimal for teaching. Simulations usually fall within two groups: specialized -which do one or two things well -- and broad -- which give a better high-level view [19,35]. The broader, more feature rich simulations are harder to use, and many do not go into the detail desired; while simpler, more focused simulations have limited use [21,41]. It can be difficult to translate knowledge from a simulation to real hardware because simulations can be imperfect, simplified, and erroneous. During research for this thesis, many simulations displayed a pattern where development would halt after some period of time, leading to a build up a bugs and incompatibility issues when attempting to run the simulations [7,10,15,16,20,43]. Large, feature rich simulations are planned and development is started, but no update or release occurs [7]. There are countless simulators to choose from, which makes evaluating them daunting. In fact, many do not meet CAO learning outcomes [19]. Students may also become frustrated if more than one simulation is used. This is due to the difficulties of managing and operating finicky simulations, which may be necessary to cover learning gaps [19].

# 3.2.3 Simulation at Louisiana Tech University

A high-level CPU simulation is currently used for Louisiana Tech University's computer architecture course. It allows students to write, modify, and run assembly code. However, this type of simulation does not allow for any observation of the workings of a processor. Additionally, the simulation does not allow for any student exploration in CPU design.

#### 3.3 FPGAs

Programs with more money at their disposal may look to FPGA boards to help students learn CAO topics.

# 3.3.1 Excessive for Some Topics

Without a sufficient background in computer architecture, students can find it difficult to use FPGAs as a learning medium without being frustrated [19]. Most successful adoptions of FPGAs as a teaching tool are aimed at senior undergraduate and graduate level students [19,21,37]. Due to the nature of FPGAs, they do not help in highlighting the link between system operations and underlying hardware circuitry. The problem with FPGAs is that they still introduce an abstraction layer, and while they help students apply advanced computer architecture concepts, learning may be hampered by the additional abstraction [20]. Additionally, FPGA boards become out of date and must be regularly maintained, replaced, and upgraded [19,39].

# 3.3.2 <u>Great for Advanced Topics</u>

FPGA boards are good for designing a CPU for an advanced, course long project, but not so much for teaching basic or fundamental topics. Advanced students prefer hands on learning and are not frustrated with the FPGAs because they have enough background courses completed to leverage them effectively [21]. FPGAs can be leveraged to teach more advanced concepts, such as parallel architectures, performance measurements, caching and memory management, pipelining, and more [37]. Students can get hands-on experience with these concepts without having the large overhead needed to use advanced simulations. This learning continues the process of demystifying the computer and helps students understand the complexities of the computer.

#### **3.4** Architecture

Changing the architecture taught in CAO courses has become an increasingly popular option to refresh the material [5,13,25,36]. However, changing the architecture in lectures or in project material would not address student learning success in the same way that the Megaprocessor does.

#### 3.4.1 Changing Course Content

Changing the architecture only changes the content of the course. The tools and methods being used to teach the course remain the same whether they are simulations or utilize FPGAs. Because the course still relies on these tools, the deficiencies that come with using them still exist.

#### 3.4.2 Using RISC-V

It has become very popular to switch over to RISC-V architecture for the computer and CPU model [13]. A list of tools and universities that use them can be found here: https://riscv.org/educational-materials/ to further showcase. Most importantly, almost all universities listed as using RISC-V, if specified, are still using simulations and FPGAs. They typically use a simulation of a RISC-V based CPU [5,13,25] or FPGAs to design RISC-V based CPUs [36]. The issues with learning

through simulations and FPGAs still exist, even if the architecture has been switched to RISC-V.

### 3.5 Novel Approaches

Educators and universities continue to search for better ways to teach computer architecture. One university took issue with how simulations can be difficult to setup and operate. This university restored and now uses over 200 old computers to explore concepts in computer architecture [41]. Another university took issue with simulators, stating that while they are useful and one of the best approaches for teaching computer architecture, they fail to convey concrete concepts. This university now uses Nintendo DS systems as a learning platform [38]. This further illustrates the educational gap between simulations, FPGAs, and achieving learning objectives in CAO.

# 3.6 Megaprocessor

The Megaprocessor can be used to fill the learning gaps left by other tools. It can become part of a larger learning pathway where simulations are used for basic level topics and digital design, the Megaprocessor is used for introductory classes on CPUs and computer architecture, and FPGAs are used for advanced topics and large projects.

# 3.6.1 <u>Suitable Subjects</u>

#### *The Science of Computing and Digital Design*

Because the Megaprocessor is built from transistors, and no obfuscation is occurring, it can be leveraged for basic and foundational concepts in digital design. It is possible to view the various gates and the circuits they are composed of. This provides students with a simpler presentation to build foundational skills so that the scale and complexity of the Megaprocessor does not overwhelm them.

#### Computer Architecture

The Megaprocessor is a fully functional and self-contained CPU. Because of this, it has the complexity necessary for a computer architecture class. Students can write code, test it with the Megaprocessor simulation, and then run their code on the Megaprocessor. The completed design and schematics are fully accessible, easy to read, and transparent. Because of this, topics including the building blocks of a CPU and CPU design can be taught well. There is no abstraction layer between the student and the underlying architecture of the CPU that there is with simulations and FPGAs. Students can learn the CPU model and its components while having access to the real computer it is based on.

### 3.6.2 <u>Unsuitable Subjects</u>

#### <u>Advanced Computer Architecture</u>

Because the Megaprocessor is not easily modified, it cannot be used as a tool for student project-based learning on CPU building. Also, it cannot be used to cover topics in Advanced Computer Architecture such as pipelining, multicore, or advanced memory configurations. Admittedly, these topics are better covered with FPGA based projects. Students will be able to experiment with different processor designs and advanced features using FPGAs, as graduate students typically have the background necessary to use them efficiently. The Megaprocessor may be suitable for this course when new PCBs are being designed and created to upgrade it, which is further explained in chapter eight.

# **CHAPTER 4**

# MEGAPROCESSOR BUILD PLANNING

#### 4.1 Establish Communication

The first step to build a Megaprocessor "clone" at Louisiana Tech required establishment of communication with the creator and designer of the original Megaprocessor, Mr. James Newman. Mr. Newman was kind enough to give his blessings and offered to assist in any way that he could. There was a great deal of communication between Louisiana Tech University and Mr. Newman in the initial months, often with a significant delay due to time zone differences (Louisiana Tech University is in Louisiana, USA, while Mr. Newman is in Cambridge, UK).

### 4.2 **Review Existing Documentation**

As the documentation published on Mr. Newman's website, www.megaprocessor.com, was examined, it was discovered that there was a significant lack of documentation on the design and methods used to build the Megaprocessor. Furthermore, there would need to be a significant reverse engineering of the design before the build could proceed. Correspondence was maintained during this time, and Mr. Newman was gracious enough to provide many additional notes and supporting documents. Significant effort was put in to planning the project from the very beginning. Unfortunately, issues continued to arise despite careful and detailed plans.

# 4.3 Create New Documentation

All the PCBs schematics were inspected, and all PCB and other images were reviewed in order to create a complete list of parts that needed to be ordered. There were many additional parts required that would not be part of the PCBs, and much work was done to ensure that nothing was missed. Detailed notes were compiled and crossexamined by the computer science department chair. The better part of a year and a half was dedicated to reverse engineering and documenting improvements before it was possible to place orders for parts. By the end of the reverse engineering phase, thorough documents (largely in the form of spreadsheets) containing everything needed to build the Megaprocessor were created. All these documents will be part of the open repository detailed in chapter six.

#### 4.4 Find and Correct Errors

During the reverse engineering process, issues with some of the PCB designs were discovered. Some of these defects were documented by Mr. Newman; however, they were only noticed during his build phase, and he corrected them with manually soldered wires. The circuit design files were corrected before the orders took place – one of the contributions to the Megaprocessor.

# 4.5 Place Orders

Placing orders was a monumental effort. Mr. Newman provided a certificate showing that one firm in the U.K. held the rights to manufacture the Megaprocessor boards. The total cost of the PCBs was approximately \$6,000 US. For the electronic components, a bidding process was required by the university. The cost of electrical components was approximately \$30,000 US. The hardware was obtained through a

university contract with Grainger. The total cost of hardware was approximately \$10,000 US. In total, the Megaprocessor build at Louisiana Tech University cost approximately \$50,000 US (so far).

#### 4.6 Creation of Simulations

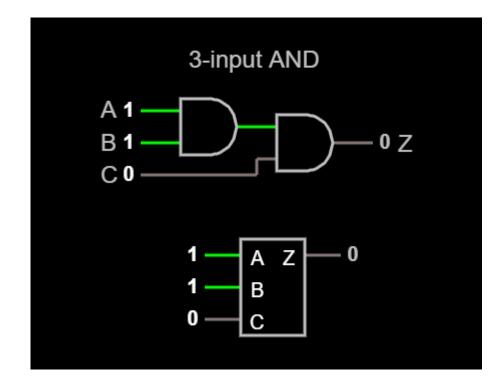

During the reverse engineering phase, something unexpected occurred. Upon reviewing the circuit designs, it became apparent that a better way to showcase them to students other than using the schematic files was necessary. As a result, a set of simulations were created (another contribution to the Megaprocessor) that utilize an online simulation tool called CircuitJS (see https://www.falstad.com/circuit/circuitjs.html, for example). A set of simulations for teaching fundamentals and gates was created. Additionally, several simulations of PCBs from the Megaprocessor were designed. The CircuitJS simulation allows for the design of complex circuits. A circuit design can be encapsulated into a component. These new components provide the functionality of the circuit but are easier for the simulation to run. The new component can then be selected like any other provided component and can be combined with other parts to create a more complex circuit. Like the rest of the outputs of the project, these simulations will be made available in an open repository.

**Figure 4-1:** The 3-input AND simulation. The top section is the circuit, the bottom is the encapsulated component.

An example of one of these simulations is a 3-input AND gate as shown in (**Figure 4-1**), that contains a circuit for the gate and a component of the encapsulated circuit displayed below it.

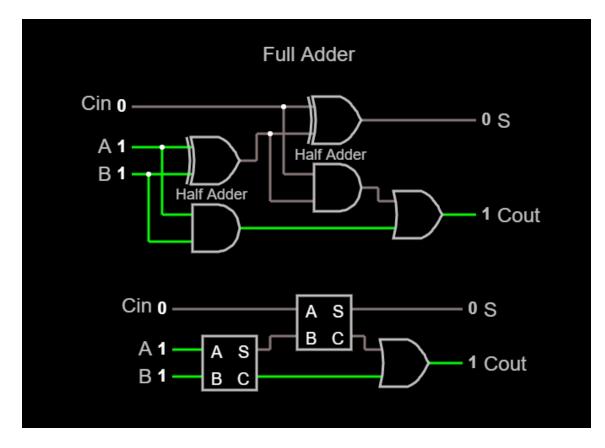

**Figure 4-2:** The Full Adder simulation. The top section is the circuit, the bottom is the encapsulated component.

Another example is a Full Adder which, like the previous example, has the gate

based circuitry with an encapsulated component below it as shown in (Figure 4-2).

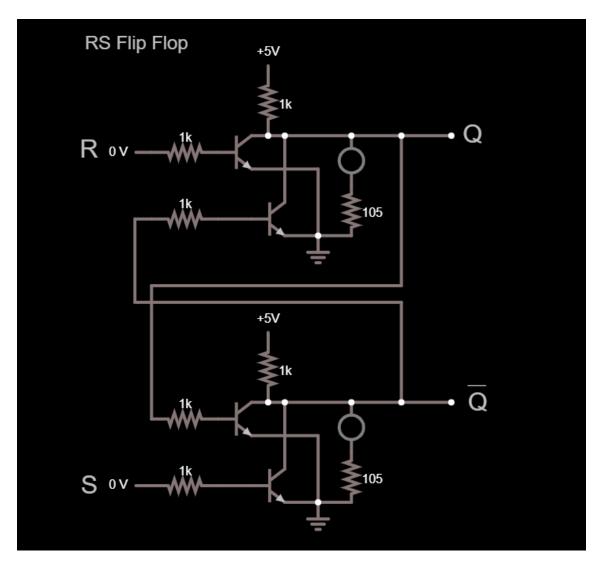

Figure 4-3: Transistor level RS Flip Flop.

As previously mentioned, it is possible to generate a circuit on the transistor level as seen in (**Figure 4-3**).

# **CHAPTER 5**

# BUILDING

#### 5.1 Soldering

In total, there are approximately 900 individual PCBs that form the Megaprocessor. To get these soldered required a significant team effort. A large room was located to house the Megaprocessor and provide a build environment, and ten soldering stations were setup. Initially, simple test PCBs were purchased from Adafruit to give students something to practice soldering on [3,4]. The initial soldering team was comprised of approximately 20 students. This number fluctuated as enthusiasm for the Megaprocessor project rose. There is a total of 300,000 solder joints for the build. This was estimated to take approximately 1,200 person-hours, provided the average solder joint takes 15 seconds (this was researched as well). The RAM is by far the most complex and difficult PCB to solder, and all 32 RAM boards account for over half of all the soldering.

#### 5.2 Testing

Due to the large number of PCBs and the daunting prospect of debugging problem PCBs down the line, testing methods were meticulously designed. The goal was that PCBs would not be accepted as 'completed' until they were tested. This would help to avoid a mountain of problem PCBs to debug at the end of the soldering phase. Initially, a testing harness was designed on large breadboards with pogo pins that could be inserted into the breadboard and stick out, exposing contact points. The PCBs would be centered in the breadboard, with pogo pins underneath each input, output, ground, and power input. A Raspberry Pi would serve as a driver, and have a ribbon cable connected to the breadboard, breaking out to all the test loops. However, an issue was discovered with this testing method. After PCBs were soldered, it was not possible to test in this way because of the test loops on the PCBs. To continue testing, the test loops would initially need to be excluded. The PCBs could then be tested, and subsequently the test loops could be soldered onto the PCBs. Ultimately, a different method was utilized that made use of testing clips (alligator clips) to connect to the test loops (that were soldered on all the inputs and outputs). Fortunately, this method became an easier testing method, though the cost of the pogo pins was ultimately lost.

Once a PCB was connected and ready to test, Python scripts that were designed at Louisiana Tech University were executed to test the PCB. These test scripts were written by students and faculty working on the project. These students also helped to identify issues in the initial testing setup and helped to create a working test setup as described above. The test scripts iterate through all the possible combinations of inputs and observe for the correct output(s). There is a known issue for larger PCBs that have too many inputs and outputs for a Raspberry Pi to connect to. To address this, multiplexors were used. Not all PCBs can be tested in this way, and time will tell if there are issues with these PCBs as the build progresses.

# 5.3 Laser Paneling

Instead of printed paper glued to wood panels for the modules (as Mr. Newman implemented in his original Megaprocessor), a laser etched design on lauan wood paneling was chosen for a more polished appearance. After some testing and debugging, an attractive product was attained (**Figure 5-1**).

Figure 5-1: Test of laser printing of module graphic.

However, a problem exists with this approach: there is a maximum size that the laser printers on Louisiana Tech's campus can support (two by four feet), and some modules that exceed that size. However, modifications can be made to the metal framing to accommodate a split in oversized modules. This would allow smaller sections of a module to be lasered and subsequently assembled onto the frame. The process of building the frames is ongoing; therefore, results on such a method has not yet been determined.

#### 5.4 Metal Framing

The metal framing was redesigned (a contribution to the Megaprocessor) that supports the ability to split the modules if needed. The metal framing for the Control and I/O frame was cut, counterbored, and assembled. To save time, the remaining metal work may be outsourced to the distributor of the extruded profile aluminum that is used in the frames. The updated frame designs will also be included in the open repository.

### 5.5 Assembling

Once ready, PCBs will be mounted onto modules. The PCBs will then be connected using ribbon cables and individual wires as needed. Most modules that have connections to others have bus connectors at the perimeter. Modules will then be mounted onto the frames. They will then need to be connected and cable managed. Some cable management is done behind the frames such that the individual wires are routed behind the PCBs and modules so that they do not obstruct viewing. Due to the silk screening of circuits on the PCBs and lasering of connectivity on the modules, tracing the connectivity diagram is easy; therefore, the wires being routed behind and hidden provides a more professional presentation. This can be seen in (**Figure 5-3**) [29].

Figure 5-2: The front of the State Machine Frame.

Figure 5-3: The back of the State Machine Module.

There is also power management to be considered at this point. Each frame can have as many as three 5-volt, 5-amp PSUs to power them. Most of the power needed for the Megaprocessor is for the 10,548 LEDs. Most connections between the frames are done over a 64-bit ribbon cable that combines buses together on one cable to allow for better cable management. All the connections will need to be made while double checking that there is not a bus being flipped and that all connections are properly seated. This, of course, is a task to be done after completion of the build phase.

Creating the custom ribbon cable should be done with caution, making sure that connectors are facing the correct way and are seated properly. A testing rig was setup to make sure that all the connections in the created ribbon cables are functional.

### 5.6 Awakening

After the Megaprocessor is built, it will take considerable effort to debug issues that arise once power is connected and it is turned on. Any number of problems could occur, including broken components, bits being flipped, and timing issues with the oscillators. Setting up the laptop and the programming of the three Igor boards on the Control and I/O boards is not a small matter. The programming of the PIC (peripheral interface controller) on the display boards, which drive the individual seven segment displays, is also something has not yet been addressed.

# **CHAPTER 6**

# PRELIMINARY RESULTS AND CONTRIBUTIONS

This project is currently still in development. The end goal is a fully functioning Megaprocessor that can be used as part of the curriculum at Louisiana Tech University – and, eventually, at other institutions throughout the world. This chapter discusses contributions to advancing computer architecture education. In summary, it details the development of a replicable build process for the Megaprocessor, as well as the merits of its use in computer architecture education. Over two years of work has gone into this project so far, with the goal of others being able to utilize the work done here without having to do their own discovery and reverse engineering process.

#### 6.1 Board Designs

All changes that were made to correct the PCB designs were documented into new PCB schematics. The revised designs are available to use for manufacturing additional PCBs.

Ten PCBs were updated: 2x2AND\_OR, 4OR, 7SEG\_3X2DIGIT, 7SEG\_METER, 7SEG\_STATUS, 8B\_RAM, 8BIT\_ADD\_SUB, 8BIT\_LOGIC, 8x2AND\_OR, and 16REG. Some required creation or correction of traces. Others required more trivial updates, such as moving a component to a better location. Two modules were also updated: Instruction & Fetch and Special Purpose Registers. Upon double checking the designs, it was noticed that there were bus boards and connections missing from the design file which were present in Mr. Newman's Megaprocessor. After consulting with him, the problems were resolved, and designs updated.

### 6.2 Parts List

The parts list is the most visible output from the significant reverse engineering process. A parts list did not exist before the start of the project. A full parts list for all the PCBs, frames, and additional hardware will be made available in an open repository. Through the build phase, many issues were encountered; therefore, many changes were made. These have all been recorded. It is the intention that the parts list that was designed be used as a basis for others to build their own Megaprocessor.

#### 6.2.1 Board Components